Memory Mapped IO란?

주기억장치들의 일부 주소를 입출력장치에 할당하는 방법으로,

해당 방식은 별도의 하드웨어 신호핀을 두지않고 Address line에 따라 분기하여 하드웨어에 접근하는 방식이다.

특징으로는

- 메모리 일부 공간을 I/O 포트에 할당

- 메모리와 입출력 번지 사이의 구별이 없음

- 메모리 명령으로 사용 가능

- 기억장치 이용 효율이 낮고 (I/O 포트가 주소영역을 공유하기 때문에) H/W가 간단

상대되는 방식으로는 I/O Mapped I/O가 있다

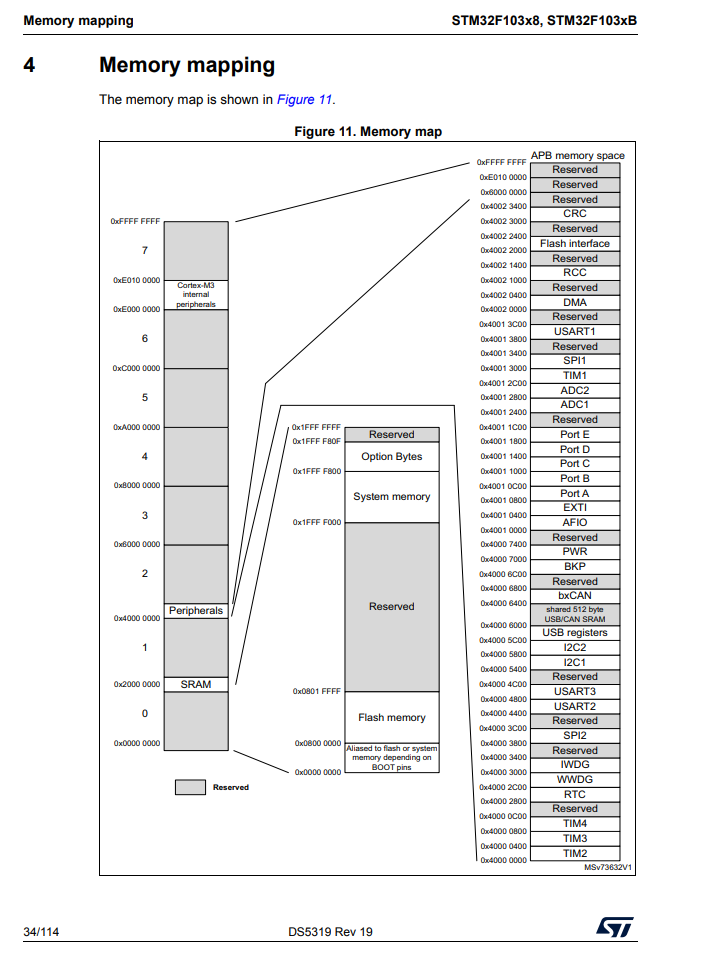

STM32F103RB 기준으로 확인하기

임베디드 프로그래밍에 사용되는 ARM 프로세서는 memory mapped I/O 방식을 사용한다.

SSAFY 수업에서 사용했던 STM32F103RB 기준으로 설명해보겠다.

STM32F103RB

- referenece manual

- datasheet

datasheet에서 Memory mapping 부분을 확인하면 메모리가 어떻게 사용되는지 확인할 수 있다.

주소가 낮은 곳에 시스템과 기억장치가 맵핑되어 있고,

주소가 높은 곳에 입출력관리 및 peripherals(주변장치)가 메모리에 맵핑되어 있는 것을 확인할 수 있다.

많은 임베디드 시스템에 사용되는 memory mapped i/o 방식은 메모리에 맵핑된 해당 장치의 레지스터 직접 접근하여 제어한다.

제어 방법은 referenece manual을 참고하여 해당 레지스터에 값을 입력하는 방식으로 제어할 수 있다.

만약 port A의 GPIO를 제어하고 싶으면 referenece manual의 3.3장 Memory map에서 base address를 찾고

원하는 설정 값에 따라서 base address + offset 주소에 설정 값을 넣어주면 제어할 수 있다!

'Computer Science > 임베디드' 카테고리의 다른 글

| 임베디드 개발 영역 (1) | 2024.12.13 |

|---|---|

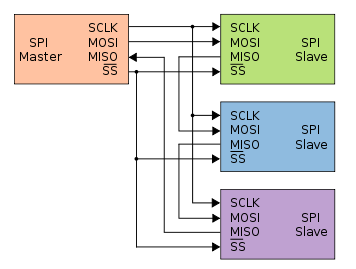

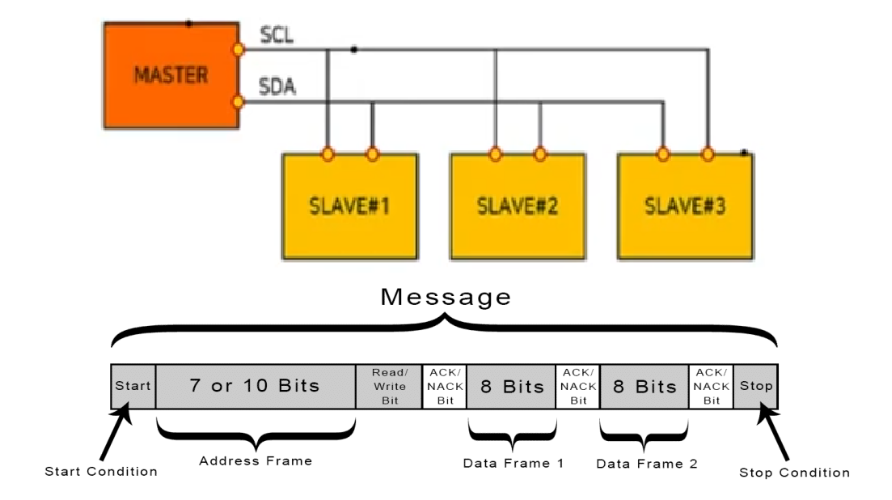

| 유선 통신 기초 (0) | 2024.08.19 |